【TSV 半導体】貫通電極で高機能・高次元化が期待!技術の現状や課題、弊社の技術をご紹介

技術コラム #01

TSVは半導体の3次元実装に重要な技術!現状と課題についてご紹介

TSVは近年、半導体の3次元実装で注目を集めています。

近年の半導体開発の動向より、IC(集積回路)の高集積化は3次元に実装する方向に開発が進んでいく見込みです。

その際に、TSV(シリコン貫通電極)などの基板の垂直方向に電極を形成する技術は、半導体分野の3次元化に大きく貢献することが期待されます。

半導体分野の動向から、TSV技術、そして弊社EBINAXが開発している「ガラス貫通電極(TGV)」についてご紹介いたします。

半導体の開発は3次元実装の方向へ

半導体業界はトランジスタの発明により大きく進展し、その後もムーアの法則(簡単にいうと、シリコン上に集積される素子は毎年2倍ずつ増加する)に沿うように、トランジスタの低価格化とそれらを有するIC(集積回路)の高集積化により成長しました。

ICの集積化は、その素子の数によりLSI(Large-Scale、大規模集積回路)、VLSI(Very Large-Scale Integration、素子が10万~1000万個)、更にULSI(素子が1000万個以上)、2000年代ではシステムLSI(超多機能LSI)と飛躍を遂げています。

これまで、IC上の半導体パッケージ部品は、主に配線を“微細化”する方向へ大きく進んできました。

一時は配線幅20nm辺りが限界と言われたこともありましたが、トランジスタの構成材料の変更や、EUVリソグラフィの実用化により10nm以下の配線も現実となり、更なる微細化が進められてきました。

しかし、原子より小さいサイズでの配線は不可能であるため、2次元での微細化配線に限界が存在するのは確かで、これ以上のトランジスタの特性向上は現実的にも厳しくなってきており、開発や製造時のコスト回収も難しくなる見込みです。

そこで近年では、実装技術の開発が重要視されるようになりました。

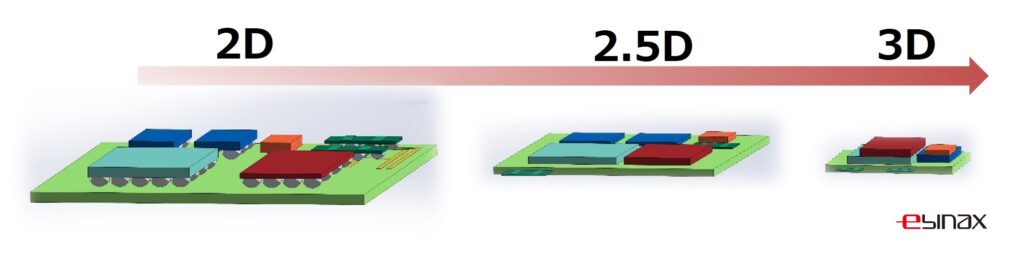

ICは3次元方向へ実装する形で更なる高集積化が進められており、高周波向けやパワー半導体などの研究が期待されています。

半導体の3次元実装に重要な技術!

半導体の2.5次元実装といわれる構造では、プリント配線板(PWB)上にインターポーザ等を介して、ロジックとメモリが実装されるモデルが一般的です。

既にワイヤボンディング等で3次元方向へ実装する半導体デバイスは量産されていますが、TSV(シリコン貫通電極)のような基板の両面に電極形成が可能な技術は、理想的な3次元技術と言われています。

それは、各媒体を貫通電極にすることで、インターポーザを介さない直接的な実装が可能となるためです。

EBINAXでは、このTSV技術を応用した「ガラス貫通穴電極(TGV)」を開発しています。

TSV(Through-Silicon Via、シリコン貫通電極)とは?

TSV(Through-Silicon Via、シリコン貫通電極)とは、シリコン基板の垂直方向に形成された貫通穴に導電性が付与されているものを表します。

多くの半導体チップの信号の授受は、シリコン製基板の表面上の金属配線で行われます。

TSVは基板の垂直方向が貫通電極として導通が得られるので、ワイヤ等を介すことなく、基板の両面に“直接”配線の形成が可能となります。

TSVの開発背景

TSVの構想は1980年代からあり、1990年代から様々な技術を用いて試行錯誤しながら開発が始められました。

しかし、従来の半導体製造工程は、ウエハプロセス(前工程)と実装プロセス(後工程)が分離していたこともあり、ウエハプロセスの段階で加工が必要となるTSVの概念は受け入れ難く、両プロセスでの連携も必要となるため、その開発が急速に進むことはありませんでした。

2000年代に入ると、ICの集積化として配線を“微細化”させる方向で進められていた開発に限界が見えてきこともあり、立体的に配線をする“3次元実装”が可能なTSVの構造が半導体業界で注目され始めました。

この頃からシリコンインターポーザ等の研究も行われ、「TSV=3次元構造」という認識が広がってきました。2012年に台湾のTSMC社がTSVで量産を開始し、TSV構造への期待は高まっているといえます。

TSVの半導体におけるメリット

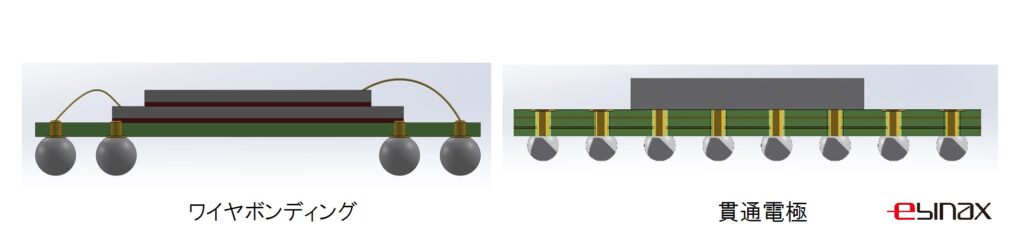

従来のシリコン製半導体チップは、ワイヤボンディング等のように、ワイヤ等で表裏の面を介さない限り、シリコン基板の片面上でしか配線が形成できませんでした。

この従来の3次元実装といえるワイヤボンディング方式では、チップとインターポーザを繋ぐ金属線(Cu、Au、Al等)の両端をボンディングする必要があり、その必要面積を確保するためにパッケージ基板の面積は大きくなる傾向にありました。

しかし、TSVのような貫通電極であれば、ワイヤの結線空間を確保する必要がなく、ボンディング部分の面積も不要となります。

通常のパッケージではインターポーザ等の仲介層を必要としますが、TSVのような貫通電極の構造があればこれらのパーツも不要となり、部品点数が削減できます。

ワイヤボンディングよりも貫通穴の方が狭い間隔で形成可能なため、面積に対する配線数を増やすことができ、3次元実装におけるパッケージ全体の小型化にも大きく貢献します。

さらに接続距離が短くなることでノイズ等の影響が軽減し、回路の高動作化など、性能面の向上も期待されています。

TSVの作製プロセス

TSVの作成プロセスは、近年開発が盛んに行われているため、様々な種類があります。

ここでは開発初期の一般的なTSVの作製プロセスを簡単にご紹介します。

基板の穴形成と導電体付与のどちらの工程を先に行うかによって、大きく2種に分類できます。

(※EBINAXでの工法は後述します。)

(1) Via first

ウエハプロセスより前にTSVを形成する工法です。ウエハプロセスでの温度に耐える必要があるため、導電体としてはリンをドープしたポリシリコンが使われます。

最初からチップデザインの設計が必要となりますが、より微細な貫通穴が作製可能となります。

(2) Via-Middle

Via firstとVia lastの中間の工法といえ、ウエハプロセス中のトランジスタ形成後にTSV構造が作製され、その後に積層の配線が形成されます。導電体の材料としては CuやW が用いられます。

(3) Via last

ウエハプロセスの後にTSVを形成する工法で、導電体としては導電ペーストやCu(Cuめっき)が利用されます。

穴加工をどちらの面から行うかで、デバイス面からの場合はFront Via(フロント・ビア)、裏面からの場合はBack Via(バック・ビア)と呼ばれ、従来の製造工程に適用しやすい手法です。

TSV(半導体)の現状の課題について

TSVは半導体産業において注目を集めている技術ですが、どのような課題があるのでしょうか。

TSV構造のメリットを最大限に活かし、大量生産を実現させるには、当然ながら技術的な課題を上手く解決し、最適な構造や製造方法を検討しなくてはなりません。

従来の集積化や実装技術にはない技術として、TSV の形成、微細金属マイクロバンプの形成、ウエハの薄層化工程、チップの張り合わせ技術などの新しい技術の開発が欠かせません。

それぞれのプロセスに課題は存在しますが、大きく2つの項目についての概要をご紹介します。

TSVの製造コスト

まず最も懸念される事項として、TSVの製造コストが挙げられます。

これまでの半導体の開発が配線の“微細化”の方向に飛躍したのも、コストが理由ともいえるでしょう。

まずはハイエンド機種向けに適用されますが、徐々にローエンド機種へ普及させるには既存パッケージと同等以下のコストが望まれます。

TSVを形成するために様々な加工工程が加わるため、積層の前に不良チップを除く必要があるなど、従来の半導体製造プロセス自体を大きく見直す必要が出てきます。

高積層化による熱の発生

TSVの形成により3次元実装が可能になると、当然ながら高積層化の状態となります。

チップ等が密集した状態だと、デバイス駆動時に発生する熱が発散しにくくなるため、熱を効率的に逃がして温度上昇を抑える必要が生じます。

TSVの電極の導電体としてCuが注目されていますが、チップの温度が上昇すると、基板のSiとCuの熱膨張系数の差により貫通穴周辺に応力が発生してしまいます。

応力が発生するとゲート特性が変化してしまうため、TSV周辺にはゲートが形成できず、トランジスタ等の活性素子は配置できない状態となります。

さらに生じた熱によりCuが膨張することで、シリコンのチップ表面から貫通穴の外側に向かってCuが飛び出すような現象(pop-up)が生じ、他のチップへも力がかかってしまう可能性があります。

またCuはトランジスタの近くに配置され、半導体の特性劣化を引き起こす可能性が懸念されるため、基板のシリコンへの拡散を抑えるような構造や技術が必要になります。

導電体となるCu以外の材料では抵抗が大きくなることが懸念されるため、チップ辺りの実装に有効な面積を増やすために、更なるTSVの貫通穴の直径の微小化が求められています。

TSV以外の貫通電極の種類と、違いについて

TSV以外の貫通電極として、TGV(Through-Glass Via、ガラス貫通電極)が挙げられます。

これまでTSVについてご紹介しましたが、それに匹敵する技術として半導体業界で注目されているのがTGVです。TSV以外の貫通電極として、TGVについてご紹介します。

TGV(Through-Glass Via、ガラス貫通電極)とは?

一般に、TSVの素材であるシリコンをガラスで代替したものを、TGV(Through-Glass Via、ガラス貫通電極)といいます。

ガラス基板に対して「貫通電極」の構造が形成されたものを表すケースが多いですが、作製手法はTSVとは大きく異なる場合があります。

TGVのメリット

TGVの貫通電極の構造がもたらすメリットは、TSVと同様だと考えられます。

ガラスの素材がもたらす特性として、シリコンよりも高い加工性を有するため、結果として半導体などの製造コストが安くなることが期待されています。

シリコンは微細加工しやすい材料として既に広く使用されていますが、ガラスは大型ディスプレイ等にも利用されているため、大型サイズでの製造が可能となり、薄いガラスの製造も可能なため、シリコン基板の厚みを削るための研磨工程は必要なくなります。

シリコンのように微細加工を施せる可能性も十分に秘めているため、実装基板の材料としての利用が期待されています。

例えば弊社のガラス貫通穴プロセスでは、内壁が平滑なφ30μmからの貫通穴を、秒速5000個/秒で穴改質し、ウエットプロセスを組み合わせて一気に処理することが可能です。

さらに、シリコンは半導体であるために伝送損失が大きく、高周波信号での使用には向きません。

ガラスは非常に平滑な表面を有し、用途に応じた組成の変更が可能なため、高周波向け材料として性能を向上させる可能性があります。

EBINAXの技術「TGV(ガラス貫通電極)」について

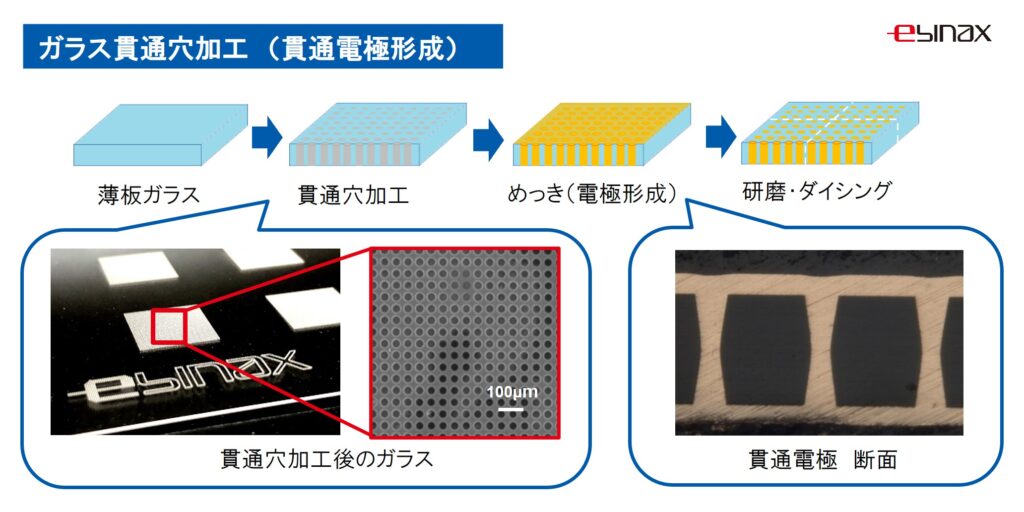

TSVやTGVのような貫通電極の構造をガラスに作製するプロセスを、EBINAXでは開発しています。

この貫通電極はガラスに貫通穴を形成し、Cuめっきで導電性を施すことで作製されます。

ガラスという素材と貫通電極の特性を活かし、TSVが活用されているインターポーザの代替としてだけではなく、高周波向けのプリント配線基板としての利用など、幅広い用途が期待されています。

■微細で多数の穴加工が可能

弊社のガラス貫通穴加工は、5000個/秒を一度に改質し、ウエットプロセスにより同時に、そして内壁が平滑な貫通穴の形成が可能です。穴径は30μmから、処理はクリーンルームで行っています。

■貫通穴への導電体付与(Cuめっき)

貫通穴の加工から導電体の付与まで、すべて弊社内で対応可能です。

貫通穴を完全に覆うCuフィリングめっき、完全には塞がずに穴の側面に沿って成膜するCuコンフォーマルめっきなど、お客様のご希望に合わせて対応いたします。