半導体にもめっきが重要!デバイスの小型化・集積化を実現するEBINAXの先端技術をご紹介

技術コラム #02

弊社、EBINAXは機能めっきを得意としている会社で、半導体へのめっきが可能です。

今回は近年ますます必要性の高まっている”半導体”をテーマに、めっき加工の重要性(役割)、弊社の加工技術についてご紹介します。

半導体とめっきの関係性とは?めっき会社のEBINAXが解説します!

半導体とめっきは、どのような関係があるのでしょうか。

「半導体」は、スマートフォン・家電製品・自動車といった個別の製品のみならず、エネルギー・通信インフラなどにも利用されており、現代社会を支える必要不可欠な要素となっています。

めっきは、「半導体」を製造するための工程の一つでもありますが、この「半導体」を製造するための装置や検査装置の部品にも適用されています。

ここでは、広く「半導体産業」で利用されているめっきの技術についてご紹介します。

半導体について

半導体の定義や製造方法などについて解説します。

半導体の定義

半導体とは、特定の電気的性質を持つ物質や材料のことです。電気を良く通す「導体」と、電気をほとんど通さない「不導体」の「中間の性質」やその性質を持つ物質のことを示します。

半導体は材料の組成や温度によって性質が変化し、例えばSi(シリコン)にB(ホウ素)やP(リン)等の不純物を加えることで、電子の流れを調整することができます。

半導体とは

半導体の性質は電子部品の動きを制御する上で非常に効果的ですが、最近では、この半導体を材料として用いた電子デバイスのことを単に「半導体」と呼ぶケースが多くなってきています。

シリコン等の材料を基本とした電子回路の構成要素は「半導体素子」といいます。

これに、電気を制御する回路を形成した電子部品を「半導体デバイス」といい、トランジスタ、ダイオード(整流器)、コンデンサ、コネクタ部品など、何万種類も存在します。

これらを集積回路にすることで、情報の記憶や論理演算がなどの知的な動作が可能になります。

そして、この半導体デバイスの弱点を補完し、外部環境から保護する技術を「半導体パッケージ」といいます。

半導体の製造方法

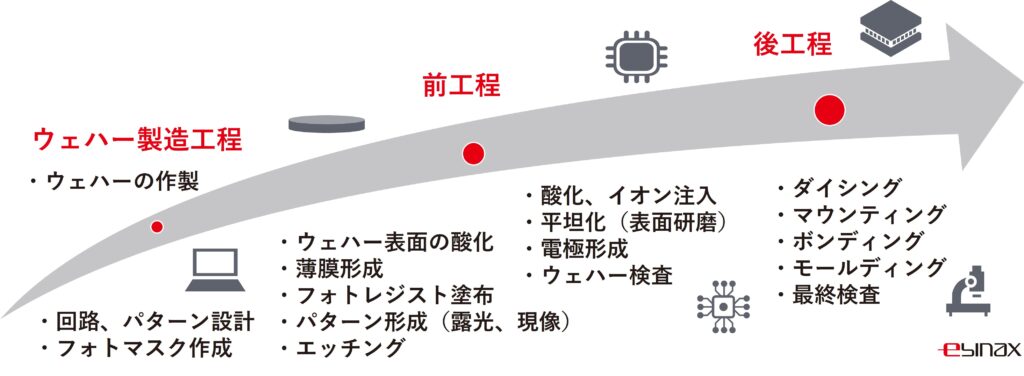

まず、目的とする半導体デバイスの機能に基づいた素子の配置と、それらを接続して回路形成するためのパターンを設計します。

この設計に基づき、インゴットから切り出したシリコンウェハーの表層に、酸化 薄膜形成・レジスト塗布・露光・現像・イオン注入・エッチング・平坦化などの処理を繰り返し行い、トランジスタやキャパシタなどの素子を形成します。

その後、各素子を多層化した金属配線で接続することで集積回路を形成しますが、ここまでの工程で1000工程以上 ときには2か月もかかって 加工されたのち、ウェハー形状での電気的な検査を行います。<前工程>。

続いて、ダイシング工程で1つ1つのチップに切断し、マウンティング工程で配線基板上に接着、ボンディング工程で電極間を接続します。

モールディング工程ではパッケージ封入していき、最終的な製品の動作や信頼性の検査・評価を行った後に出荷されます<後工程>。

各工程にも数多くの処理が必要となるため、実に長い工程を経て半導体は製造されます。

また、これらの半導体の製造には、専用の高精度な製造装置・検査装置が使用されます。

半導体の重要性

半導体は身近な電子機器から社会インフラまで、多岐にわたる分野で活用されています。

近情報化社会の発展に伴い、最新システムの開発と更新は必須であり、高度な情報処理装置や多機能な電子機器が安定的に動作することが求められています。

これらの中枢を担う半導体デバイスの製造・実装技術は、社会の発展においても重要な役割を担っているといえるでしょう。

半導体産業を支える技術「めっき」について

半導体産業において、めっき技術は重要な存在です。

半導体におけるめっきの役割や種類についてご紹介します。

半導体におけるめっきの役割とは

半導体の製造工程において、めっきは前工程から後工程、組み立て時など様々な段階で活用されています。

例えば、シリコンウェハー上に形成したトランジスタなどの素子を接続する多層配線には、銅めっき(ダマシンプロセス)が用いられています。

チップの電極には、その接合方法によって、めっきバンプや、ワイヤーボンディング用・はんだ接合用のめっき処理が施されています。

またチップを実装する半導体の回路基板側にも利用されています。

さらに、これらの半導体部品の製造や検査、パッケージング技術に用いられる、高性能な製造・検査装置にもめっき加工された部品が多数利用されています。

めっき技術は、半導体ならびにその製造プロセスに欠かすことはできないといえるでしょう。

半導体で使われるめっきの種類

ここでは、一般的な「半導体へのめっき」をいくつかご紹介します。

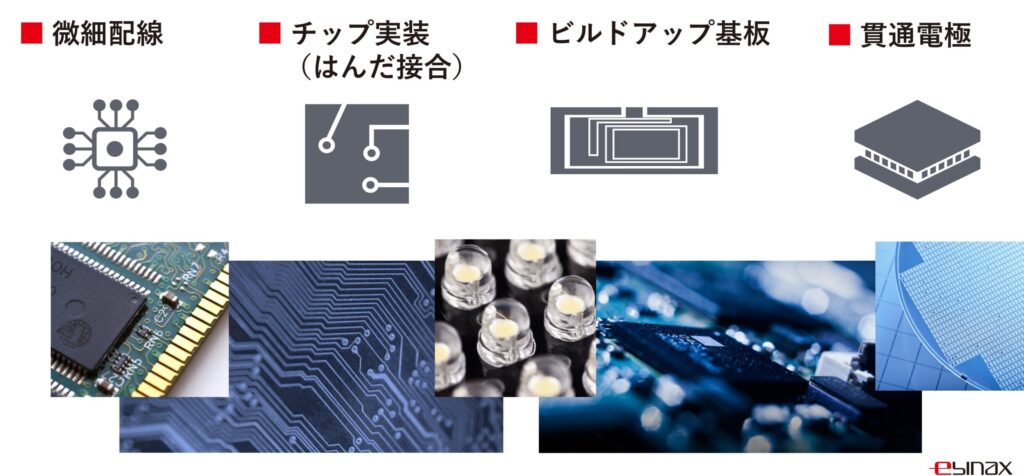

■ウェハー上の微細配線へのめっき

90年代まで、シリコンウェハー上の配線形成はCVD(化学気相成長法)などのドライ成膜によるAl系膜が一般的でした。

しかし、1997年にIBMにより「電気銅めっき」の技術とCMP(研磨)を組み合わせるCuダマシンが発表されました。

Alよりも抵抗が低く、厚膜とボトムアップ成膜により層間の接続も可能な配線形成の方法として、一気に実用化・量産化が拡大しました。

現在は、半導体メーカー(ファブ)が、前工程の専用装置にて対応しています。

■チップ実装(はんだ接合)へのめっき

半導体チップの実装には、チップ同士をワイヤーで接続するワイヤーボンディング法、接続用のバンプ(突起電極)を形成し異方性導電フィルム(ACF)で導通をとるフリップチップ法、またはんだ接合など、様々な工法が用いられています。

いずれの手法も、その接合表面には、ニッケルや金めっきなどが用いられます。

■ビルドアッププリント基板へのめっき

ビルドアッププリント配線基板は、半導体の積層ごとに上下の導体層をめっきによって接続する工法が一般的です。

表層回路の導体形成と、層間の接続孔を導電体で埋め込むことが可能です。

■貫通電極基板(TSV、TGV)へのめっき

半導体の貫通穴を形成したシリコンやガラス基板に導電体を付与する手段として、めっきが用いられています。

基板の表裏と貫通穴壁面に導体を形成することで、実装時の小スペース化が期待されます。

EBINAXのめっき技術(半導体)について

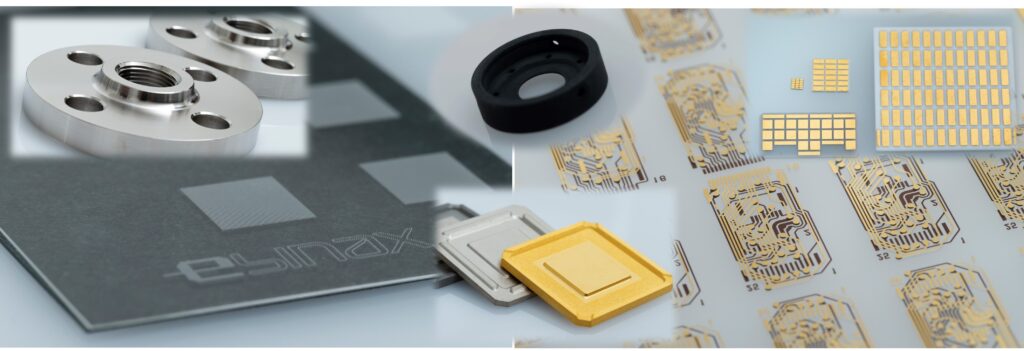

EBINAXでは、半導体の製造・検査装置に使用される部品へのめっきにも対応しています。

その半導体へのめっき技術をご紹介します。

弊社で対応可能な半導体のめっき加工について

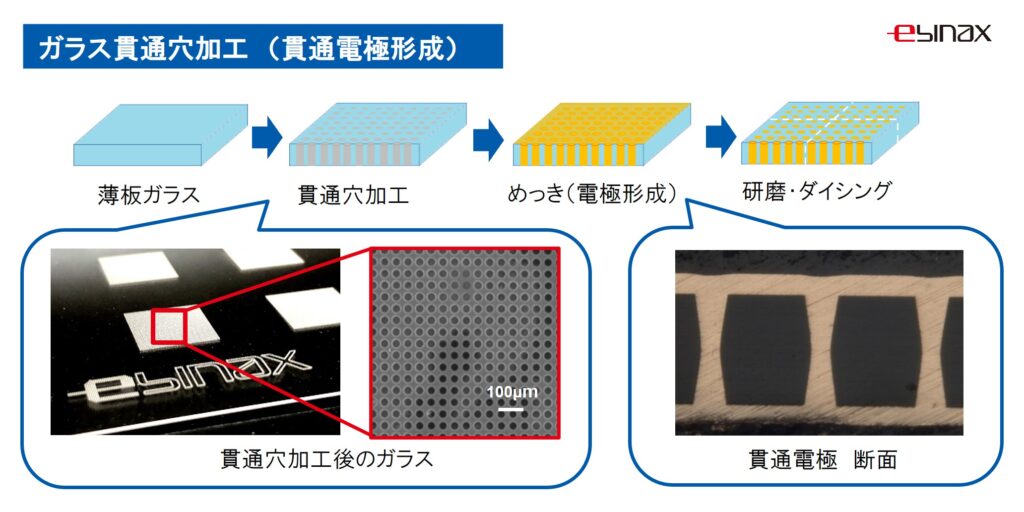

■ガラス貫通穴加工、パターン形成

平坦・平滑・高耐熱といった特性を有するガラス基板のメタライズ、導体パターン形成が可能です。

薄板ガラス基材の調達から、微細貫通穴形成、表裏面および穴内部の導電性付与(銅での穴充填)、パターニング・個片化まで弊社にて対応し、「貫通電極を有するガラス配線基板」の作製が可能です。

半導体デバイスの高集積化、3次元化にお役立てください。

■セラミックスへのめっき

放熱特性の高いセラミックスに対し、パターン形成や貫通穴への導電付与などが可能です。

LEDやLDのサブマウント基板、ペルチェモジュール用セラミックス基板等への実績があります。

■複合材へのめっき

金属と 炭素やセラミックスの金属基複合材は、放熱高熱伝導性を活かしてヒートシンクやヒートスプレッダに使用されています。

弊社では、各種複合材の組成・表面状態に合わせ、適切なめっきプロセスを構築しており、はんだ付け性・防塵性などを付与することが可能です。

■黒色めっき「スゴクロ」

めっき皮膜の表面形状を制御することで、低反射の黒色皮膜を成膜します。

半導体センサーや液晶部品等のノイズ低減・感度向上に貢献します。

■高放熱めっき「スゴヒヱ」

皮膜の表面形状を制御し、圧倒的に大きな比表面積を厚さわずか5μm以下で作り込むことで、表面に高放熱特性をもたらします。

半導体デバイスの熱対策に一役買います。

■無電解ニッケルめっき

ニッケル皮膜で部品などを被覆することで、耐食性や硬度、耐摩耗性の向上、はんだ濡れ性を付与します。

半導体の製造装置や検査装置の精密部品の処理に実績があります。

弊社で対応可能な素材(基材)

金属、セラミックス、ガラス、プラスチック、複合材、カーボンなど

弊社で可能なめっきの種類

■電気めっき

銅、ニッケル、金、銀、白金、パラジウム、コバルト、スズ、ニッケル-鉄、ニッケル-コバルト など

■無電解めっき

ニッケル、銅、金、複合、PTFE複合ニッケル、SiC複合ニッケル、BN複合ニッケル、Al2O3複合ニッケル など

半導体は三次元に!デバイスの小型化や集積化へと進化

半導体の今後の開発の方向について、そして弊社の三次元化に関する技術についてご紹介します。

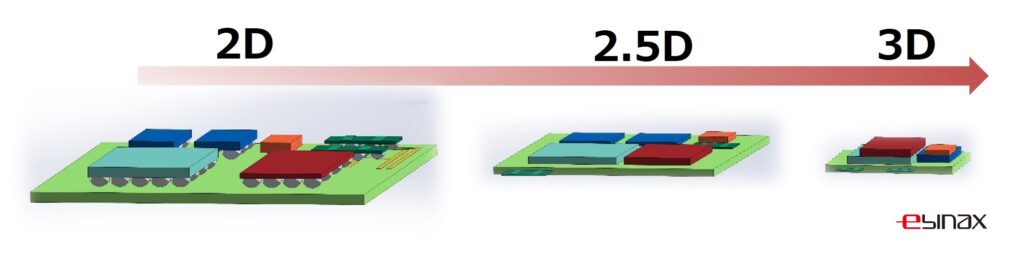

半導体は3次元化の方向へ

半導体は小型化・集積化が求められていますが、これまで進展してきた配線の微細化はコストや生産面からもいよいよ限界に近づこうとしています。

近年では、パッケージ上で半導体同士を接続する配線を形成することで集積化する、システムインパッケージ(SiP)の重要性が高まってきました。

そこで、パッケージ化した後に3次元に積層して接続するパッケージオンパッケージ(PoP)や、貫通電極を形成して3次元に積層していくシリコン貫通電極(TGV)やガラス貫通電極(TGV)の開発が注目されています。

EBINAXの3次元化技術

弊社では、「貫通電極を有するガラス配線基板」の作製が可能です。

半導体基材に貫通穴を形成し、穴の内部に導体を付与することで、高周波向けとして期待されているガラス基板の表裏の導通を可能にし、半導体の高密度化を実現します。

半導体のめっき加工のことならEBINAXにお任せください!

弊社が長年培ってきためっき技術は、半導体デバイスやその製造・検査工程に適用可能な、高い要求にも対応しています。

実際に半導体の製造・検査装置へ納入している実績もあります。

めっき技術で実現可能な導電性や放熱特性、はんだ特性の付与はもちろんのこと、半導体産業で新たな技術開発をされている方も、ぜひ弊社までお気軽にお問合せください。

<<「技術コラム」一覧へ

<<「めっきQ&A・コラム」INDEX